#### Proposed baseline for D3.0: 1

2 3

# 79.3.2.5 PD requested power value

## Not part of the baseline

The content of PD requested power value (named Y field in the adhoc material) is function of 3 use cases:

- 1. Use Y when PSE is connected to single-signature PD or Type 1 and Type 2 PDs.

- Use Y=0 when connected to dual-signature PD over 4-pirs and both modes are active. 2.

- Use Y=PD requested power Mode X when connected to dual-signature PD over 2-pairs to interoperate with PSEs operating over 3. 2-pairs.

- 4

The PD requested power value field shall contain the PD's requested power value defined in Table 79–5, for Type 1, Type 2, and single-signature Type 3 and Type 4 PDs. The fields for PD requested power value shall be set to 0 for Type 3 and

- 5 6 7 Type 4 dual-signature PD operated over mode A and mode B.to the sum of PD requested power value Mode A and PD

- 8 requested power value Mode B in Table 79-6a, for Type 3 and Type 4 dual signature PDs.

9 For Type 3 and Type 4 dual-signature PD operated over 2-pairs, the fields for PD requested power value shall be set to the

10 value of PD requested power value Mode (X) where X is the active mode (A or B).

11

# Table 79–5—PD requested power value field

| Bit  | Function                    | Value/meaning                                                                                                                                   |

|------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | PD requested<br>power value | Power = 0.1 × (decimal value of bits) Watts.<br>Power expressed in units of 0.1 W.<br>Valid values for these bits are decimal 1 through 255999. |

12

- 13 PD requested power value" is the maximum input average power (see 33.3.8.2 and 145.3.8.2) the PD is requesting. "PD

- 14 requested power value" is the power value at the PD PI.

#### 15 79.3.2.6 PSE allocated power value

- 16 The PSE allocated power value field shall contain the PSE allocated power value defined in Table 79-6 for PSEs connected 17 to single-signature PDs and Type 1 and Type 2 PDs.

- 18 The fields for PSE allocated power value shall be set to 0 for Type 3 and Type 4 dual-signature PD operated over mode A 19 and mode B.

- 20 For Type 3 and Type 4 dual-signature PD operated over 2-pairs, the fields for PSE allocated power value shall be set to the

- 21 value of PSE allocated power value Alternative (X) where X is the active Alternative (A or B).

- 22 The sum of the PSE allocated power value Alternative A field and the PSE allocated power value Alternative B field, as

- 23 defined in Table 79 6a, shall be provided in the PSE allocated power value field for Type 3 and Type 4 PSEs connected to a

- 24 dual signature PD. The sum of the PSE allocated power value Alternative A field and the PSE allocated power value

- 25 Alternative B field may be provided in the PSE allocated power value field for Type 1 and Type 2 PSEs when connected to 26 a dual-signature PD. 27

# Table 79–6—PSE allocated power value field

| Bit  | Function                     | Value/meaning                                                                                                                                   |

|------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | PSE allocated<br>power value | Power = 0.1 × (decimal value of bits) Watts.<br>Power expressed in units of 0.1 W.<br>Valid values for these bits are decimal 1 through 255999. |

<sup>28</sup> 29 30

31

32

"PSE allocated power value" is the maximum input average power (see 33.3.8.2 and 145.3.8.2) the PSE expects the PD to draw. "PSE allocated power value" is the power at the PD PI. The PSE uses this value to compute PClass defined in 33.2.7 and 145.2.7.

#### 33 79.3.2.6a Dual-signature PD requested power value Mode A and Mode B

Not part of the baseline

Baseline for review: LLDP ad hoc meeting material June 2017 Rev000

We need to delete the red text in order to allow PSE to know what is the requested power on both modes when PD switches back from 2-pairs to 4-pars.

The "Dual-signature PD requested power value Mode A and Mode B" fields shall contain the PD requested power value defined in Table 79–6a for mode A and for mode B of a dual-signature PD.

If mode (X) is non-active while the other mode is active, the inactive PD requested power value Mode (X) field value shall be set to 0.

Single-signature PDs shall set the PD requested power value Mode A and Mode B fields to 0.

## Table 79-6a-Dual-signature PD requested power value field for Mode A and Mode B

| Bit  | Function                                          | Value/meaning                                                                                |

|------|---------------------------------------------------|----------------------------------------------------------------------------------------------|

| 15:0 | Dual-signature PD requested power value<br>Mode A | Power expressed in units of 0.1 W.<br>Valid values for these bits are decimal 1 through 499. |

| 15:0 | Dual-signature PD requested power value<br>Mode B | Power expressed in units of 0.1 W.<br>Valid values for these bits are decimal 1 through 499. |

10 11

12

"Dual-signature PD requested power value Mode A" and "Dual-signature PD requested power value Mode B" are the

13 maximum input average power levels (see 145.3.8.2) the PD is requesting for the respective Mode.

## 14 79.3.2.6b PSE allocated power value Alternative A and Alternative B

15 The PSE allocated power value Alternative A field and the PSE allocated power value Alternative B field shall contain the

16 values in Table 79–6b for Type 3 and Type 4 PSEs operating over both pairsets when connected to a dual-signature PD.

## Table 79-6b-PSE allocated power value Alternative A and Alternative B field

| Bit  | Function                                   | Value/meaning                                                                                |

|------|--------------------------------------------|----------------------------------------------------------------------------------------------|

| 15:0 | PSE allocated power value<br>Alternative A | Power expressed in units of 0.1 W.<br>Valid values for these bits are decimal 1 through 499. |

| 15:0 | PSE allocated power value<br>Alternative B | Power expressed in units of 0.1 W.<br>Valid values for these bits are decimal 1 through 499. |

17

"PSE allocated power value Alternative A" and "PSE allocated power value Alternative B" are the maximum input average

power levels (see 145.3.8.2) the PSE expects the dual-signature PD to draw on the respective Alternatives. "PSE allocated

power value Alternative A" and "PSE allocated power value Alternative B" are the power levels at the dual-signature PD PI.

The PSE uses this value to compute PClass-2P defined in 145.2.7. <u>A PSE providing power to a dual-signature PD over 2-pairs</u>,

shall set 0 in the non-active PSE allocated power value alternative X field where X is the non-active Alternative (A or B).

A PSE providing power to a Type 1, Type 2, or single-signature Type 3 or Type 4 PD, places 0 in the "PSE allocated power value Alternative A" and "PSE allocated power value Alternative B" fields defined in Table 79–6b.

## 25 79.3.2.6e PSE maximum available power

#### Not part of the baseline

Power management for single signature and dual signature cares only for the total port power. Parts of the power management then use this power to allocate it per A and B fields. The following changes will allow us to get rid of the requirement of Y=A+B in D3.0 and set Y=0 instead, when Type 3 /4 PSE operating over 4-pairs is connected to dual signature.

9

The PSE maximum available power field shall contain the highest power the PSE can grant as defined in Table 79–6e to the

port when supporting single-signature PD or dual-signature PD PD. The PSE shall set the value of this field taking available

power budget and hardware capabilities into account.

#### Not part of the baseline

The following change is required to allow dual-signature PD when operating over 2-pairs to get power on the inactive pair later when the inactive pair became active. This is part of the solution to resolve comment #297.

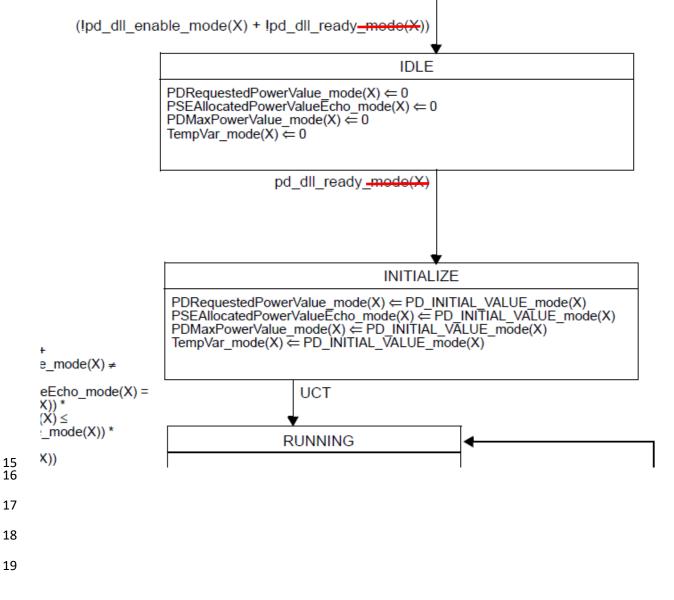

#### pd\_dll\_ready\_mode(X)

An implementation-specific control variable that indicates that the PD has initialized Data Link Layer classification. <u>for Mode(X)</u>. This variable maps into the <u>aLldpXdot3LocReady</u> <u>aLldpXdot3LocReadyA</u> and <u>aLldpXdot3LocReadyB</u> attribute (<u>30.12.2.1.20</u> <u>30.12.2.1.18a</u> and <u>30.12.2.1.18b</u>). Values:

### 8 9 10

11

12

14

4 5

6

7

- FALSE: Data Link Layer classification has not completed initialization. TRUE: Data Link Layer classification has completed initialization.

- 13 Change "!pd\_dll\_ready\_mode(X)" to !pd\_dll\_ready in Figure 145-34